[KJtimes=한이웅 논설위원] 삼성전자가 지난 6월 30일 ‘GAA 방식으로 3나노 칩 생산에 성공해 양산한다. 퀄컴으로부터 3나노 리저브(예약)에 대한 합의가 있었다’고 발표했다. 이어 7월 25일에는 3나노 양산분의 첫 출고식을 진행했다.

[KJtimes=한이웅 논설위원] 삼성전자가 지난 6월 30일 ‘GAA 방식으로 3나노 칩 생산에 성공해 양산한다. 퀄컴으로부터 3나노 리저브(예약)에 대한 합의가 있었다’고 발표했다. 이어 7월 25일에는 3나노 양산분의 첫 출고식을 진행했다. 하지만 주목할 만한 것은 삼성전자의 3나노 첫 양산분은 중국의 비트코인 채굴용 반도체(ASIC) 제조업체인 PanSemi에 공급한다고 하나 계약 규모나 공급량 등 구체적인 계약 내용은 알려지지 않고 있다는 점이다.

MBCFET 베이스의 GAA 적용에 성공‧양산하게 된 것은 매우 큰 성과

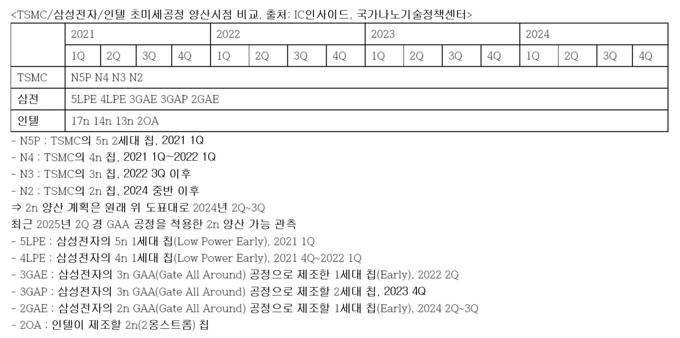

현재 삼성전자는 국내 언론들을 통해 3나노 양산과 첫 출고식 발표를 크게 알리는 등 자사가 파운드리 글로벌 1위 대만의 TSMC보다 먼저 3나노 양산에 성공, 기술적으로 게이트 올 어라운드(GAA) 공정의 채택이라는 점에서 2025년 2나노 생산에서야 GAA를 적용할 TSMC와 비교해 시간적으로 2년여 앞서나가게 됐다는 점을 강조 중이다.

또한 삼성전자 3나노 칩은 PPA 즉, 전력사용(Power)을 45% 절감하고, 성능(Performance)은 23% 개선됐으며 크기(면적, Area)은 16% 줄어들었다고 부연하고 있다.

그러나 여기서 주의 깊게 살펴볼 것이 있다. 바로 3나노 칩 관련 삼성전자가 이번 중국업체에 납품할 생산분을 ‘시제양산’이라고 부르고 본격 양산은 올 연말경 하게 될 예정이라는 대응의 의미다.

하지만 근원적 기술력이라고 할 수 있는 특허 문제와 삼성전자 3나노 칩 개선비율 비교 대상이 무엇이며 왜 중국업체에 첫 공급을 하게 됐는지, 삼성전자의 고질병인 수율문제는 어떻게 되는지, 미래 경쟁력은 긍정적인지 등에 대해서는 거의 풀어내지 않고 있어 의구심을 증폭할 수밖에 없는 상황이다.

우선 특허 문제부터 짚어보면 이번 삼성전자의 3나노 칩은 다중가교채널방식(MBCFET) 베이스의 GAA 공정으로 생산된 것으로 알려지고 있는데 나노시트를 적용해 일반 GAA 공정 시 만들어지는 채널의 면을 더 넓힌 것을 말하고 있다.

이는 일반 GAA 공정으로 3나노를 생산할 경우 대부분의 3나노 특허를 보유하고 있는 TSMC와 분쟁이 일고, 불리한 상황에 처할 것으로 보고 이를 회피하기 위해 MBCFET 베이스의 GAA 공정을 적용한 것으로 보인다.

예컨대 삼성전자가 3나노 공정에서 채택한 MBCFET 베이스의 GAA 공정은 불가피한 선택이었다는 것이다. 다만 일반 GAA 공정보다 더 어려운 MBCFET 베이스의 GAA 적용에 성공하고 양산하게 됐다는 것은 매우 큰 성과라고 할 수 있다.

다음으로 짚어볼 것은 삼성전자 3나노 칩의 개선비율 비교 대상이다. 업계에서는 이번 삼성전자의 3나노 칩은 칩 전체가 3나노로 설계된 것이 아니라 칩 설계의 약 30% 정도에 3나노 기술을 적용하고 70% 정도가 5나노로 설계됐을 것으로 추정하고 있다. 이러한 추정의 근거는 설계의 100%가 3나노로 설계됐다면 삼성전자가 발표한 개선비율보다 훨씬 큰 폭의 개선이 있었어야 한다는 것이다.

그러나 정작 여기서 중요한 것은 설계의 100%든 30%든 3나노 설계 칩을 생산 및 양산한다는 것은 큰 업적이라는 점이다. 하지만 TSMC는 ‘삼성전자의 3나노는 TSMC의 5나노와 비슷한 성능일 것’이라고 폄하하고 있다. 이는 삼성전자가 3나노에서 PPA(전력구매계약)가 개선된 비율을 비교한 대상이 성능이 안 좋다고 알려진 삼성전자의 5나노 LPE 칩이기 때문이다.

사실 삼성전자가 TSMC에게 첨단공정에서 본격적으로 밀리게 된 것이 5나노 LPE(Low Power Early, 삼성전자의 제품 약어, 5나노 초기 칩이라는 의미) 칩의 칩밀도(Peak Transistor Density)가 TSMC의 동급 칩인 N5P와 비교해 약 25% 이상 뒤처진 성능(삼성전자 130 vs TSMC 170)이었다는데 있다.

때문에 5나노 개발 전까지 삼성전자의 고객이었던 애플이 삼성전자의 5나노 LPE 보다 성능이 뛰어난 TSMC N5P를 채택했고 이후 TSMC에게 AP용 칩 오더를 몰아주면서 TSMC가 소품종 대량생산 체제를 구축하게 된 계기가 됐다.

따라서 TSMC가 삼성전자의 3나노 칩을 자사의 5나노 칩과 비슷한 성능이라고 폄하한 것은 과한 측면이 있다. 그렇지만 삼성전자의 3나노 칩이 자사의 5나노 LPE가 아닌 TSMC의 N5P와 비교해 얼마나 개선된 성능을 보이느냐를 비교한다면 다른 수치가 나오게 될 것이라는 업계 일각의 시각을 무시할 수만은 없는 상황이다.

삼성전자 3나노 칩 첫 고객이 중국업체인 이유

하지만 무엇보다 주목할 만한 것은 삼성전자 3나노 칩 첫 고객이 중국업체인 이유라고 할 수 있다.

현재 애플‧퀄컴‧AMD‧엔비디아 등 비메모리 칩의 큰 손들은 모두 TSMC의 고객이다. 이들은 현재 7나노~4나노급 칩들을 공급받고 있으며 3나노도 TSMC로부터 공급받을 예정이다.

TSMC도 3나노 공급계획과 관련 PPA(전력소모/성능/크기)가 모두 대폭 향상된 기본형과 PPA 중 특정 분야가 개선되고 1~2분야는 5나노와 비슷한 성능의 파생형 세 가지(N3E 2-1 Fin, N3E 2-2 Fin, N3E 3-2 Fin) 등 네 가지 옵션을 마련해 고객들이 자사 제품의 특성에 맞는 옵션을 선택할 수 있도록 계획을 세웠다.

이와 비교해 우리 언론에 보도되지 않았지만 업계 일각에서는 삼성전자 3나노 칩의 PPA 개선비율의 비교 대상이 무엇인지 잘 알고 있고 첫 고객으로서 ‘실험 쥐’의 처지가 되는 것을 원하지 않기 때문에 삼성전자로서는 평소라면 쳐다보지도 않을 업체를 첫 고객으로 한 것이라는 분석이 나오고 있다.

또 다른 일각에서는 3나노 첫 양산분이라는 점에서 성공사례를 실제로 보여줘야 할 삼성전자로서는 고객을 가릴 처지는 아니었을 것이라는 시각도 있다.

또한 중국업체로서는 자신들이 만드는 비트코인 채굴용 반도체가 PPA 중 특히 PP에 민감함을 감안할 때 삼성전자의 3나노 칩은 매력적으로 보여 양자가 손을 잡게 됐을 것으로 추정된다는 목소리도 설득력을 얻고 있는 분위기다.