[KJtimes=한이웅 논설위원] 삼성전자는 4나노 칩을 자사의 AP 엑시노스와 퀄컴의 스냅드래곤8의 두 가지를 생산 중이다. 이 두 가지 칩의 수율은 기업비밀이다.

[KJtimes=한이웅 논설위원] 삼성전자는 4나노 칩을 자사의 AP 엑시노스와 퀄컴의 스냅드래곤8의 두 가지를 생산 중이다. 이 두 가지 칩의 수율은 기업비밀이다. 하지만 업계에서는 엑시노스용은 25~35%, 스냅드래곤8용은 약 45% 내외이며 이에 비해 대만의 TSMC는 스냅드래곤8+용 4나노 칩인 N4 수율이 약 55% 이상인 것으로 파악 중에 있다.

삼성전자가 팰리클 사용하지 않는 이유

업계에서는 이와 관련, TSMC의 노하우 등 다른 이유도 있겠지만 퀄컴이 삼성전자의 스냅드래곤8 생산을 지켜보고 이를 개선한 스냅드래곤8+ 설계를 변경했을 것이 거의 확실하며 따라서 TSMC에서 생산하는 스냅드래곤8+용 4나노 칩인 N4의 수율이 삼성전자보다 뛰어난 것은 당연하다고 보고 있다.

그런가 하면 업계 일각에서는 5나노~4나노 칩 생산에 TSMC는 팰리클(노광공정 중 포토마스크에 먼지가 끼는 것을 방지하기 위해 그 위를 덮는 얇은 폴리실리콘 소재의 멤브레인)을 사용하지만, 삼성전자는 2023년 하반기 이후에야 팰리클을 사용할 계획인 것도 영향을 미쳤고 TSMC가 후공정에 강점이 있다는 점이 수율 제고에 도움이 됐을 것이라는 시각도 있다.

삼성전자는 비공식적으로 ‘팰리클은 EUV에 사용하는 것인데, 당사가 보유한 EUV 대수가 얼마 되지 않으며, 가격이 비싸서 이런 부분을 모두 고려해 채용하지 않은 것이다. 현재 팰리클을 사용하지 않는 당사의 초미세공정 수율이 낮을 수밖에 없다. 그러나 2023년 하반기 이후부터 팰리클을 사용할 계획이므로 결국 팰리클에 의한 수율 차이는 극복하게 될 것’이라는 반응이다.

그러나 일각에서는 팰리클은 기본적으로 투과율 문제로 수율이 낮아지고 생산량이 적게 나오는 대신 포토마스크에 먼지가 앉아 발생하는 불량을 방지하고 궁극적으로 사용하지 않을 때보다 사용하는 것이 수율이 높게 나오며, 초미세공정의 수율을 올릴 수 있다면 팰리클을 사용하지 않는다는 것은 앞뒤가 맞지 않다는 시각이 강하다.

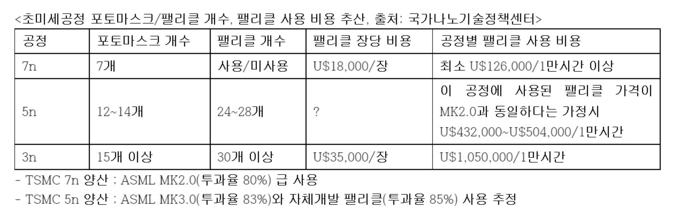

팰리클은 네덜란드 반도체 장비업체 ASML에서 2016년 투과율 78% 제품을 개발했고, 2018년 투과율 80%인 MK2.0을 공급했으며 2020년 투과율 83%인 MK3.0을 공급했고 2021년 투과율 90%인 MK4.0을 개발해 곧 양산에 들어갈 예정이다.

현재 TSMC는 ASML의 팰리클을 사용하다가 자체 개발을 시도해 2018년 투과율 85%의 팰리클 개발에 성공한 후 2019년부터 자사 팰리클을 사용 중에 있다.

ASML 팰리클 기준 사용 시간은 1만 시간이며, 팰리클 1장당 가격은 MK2.0이 1만8000달러, MK4.0은 3만5000달러 수준이다.

그런데 5나노 공정에서는 1개 라인 당 포토마스크 12~14개, 팰리클 24~28개 사용, 1개 라인 당 1만 시간(1일 24시간 기준 416일)에 43만2000~50만4000달러 비용이 소요된다. 업계 일각에서는 이와 관련, 비싸긴 하지만 수율이 삼성전자 레벨에서 TSMC 레벨로 올라갈 수 있다면 이 비용을 지불하지 않는 것이 더 이상한 일이 될 것이라는 시각이 우세하다.

따라서 삼성전자가 팰리클을 사용하지 않는 것에 업계에서는 다른 이유보다는 ▲TSMC 자체 개발 팰리클은 TSMC가 경쟁사인 삼성전자에 공급할 이유가 없으며 ▲ASML이 TSMC와 특수관계라는 점이 팰리클 공급을 어렵게 했을 가능성이 있다는 이유에 타당성을 두고 있는 모습이다.

여기에 ASML 팰리클은 ASML이 기술 등을 총괄하고 캐나다 테라다인(멤브레인)과 일본 미쓰이화학(생산)과 협업해 생산하는 것으로 삼성전자가 EUV를 사용해 7나노를 양산한 시점인 2019년 4월에는 팰리클 사용을 배제하고 생산을 시작했을 가능성이 있고, 2019년 7월 1일 한일무역 갈등이 시작된 이후에는 일본 미쓰이화학이 생산하는 ASML 팰리클을 삼성전자가 사용할 수 없었을 것으로 추정하는 시각도 있다.

삼성전자는 S&S TECH, FST, 디바이스ENG 등을 지원하며 공동으로 투과율 90% 이상의 팰리클을 개발 중으로, S&S TECH가 2021년 말 투과율 90%의 팰리클 개발에 성공해 이를 발전시켜서 양산하고 2023년 하반기부터 공정에 팰리클을 도입한다는 계획이다. 이와 관련 최초 팰리클은 ASML 도입분과 협력사와 공동 개발한 것을 병용할 것이라는 예상이다.

이외에도 국내 소부장 기업 중 참그래핀에서 2022년 상반기에 폴리실리콘 소재가 아닌 그래핀 소재의 투과율 90% 이상인 팰리클 개발에 성공했다.

팰리클은 광원이 팰리클을 통과할 때 발생하는 열에 내성을 가져야 하므로 폴리실리콘보다 내열성이 좋은 그래핀 소재가 미래 경쟁력에서 우위에 있다는 시각이어서 장차 팰리클 분야 글로벌 리더가 기존의 ASML, TSMC와 삼성전자 및 협력사, 참그래핀, 인텔이 주도하는 팰리클 개발세력 중 누가 쥐게 될 것인지도 관심사다.

삼성전자가 약점을 얼마나 슬기롭게 대처해 나갈지 초미 관심사

삼성전자의 다중가교채널방식(MBCFET) 베이스의 게이트 올 어라운드(GAA) 공정을 적용한 3나노 칩 양산은 GAA 공정의 적용이라는 측면에서는 분명히 TSMC보다 2년여 앞서게 된 가장 큰 성과다. 또한 중국업체를 통한 3나노 칩 테스트가 성공적으로 끝나면 글로벌 큰 손들을 고객으로 만들 좋은 기회가 될 것이 분명한 사실이다.

그러나 이 테스트가 성공한다고 해도 EUV 장비의 수(2021년말 기준, 삼성전자 20여 대 vs TSMC 50여 대), 생산능력(공장 수 삼성전자 6개 vs TSMC 18개), TSMC의 4나노~5나노 제품이 수율과 성능에서 삼성전자 동급 칩을 앞서는 점, TSMC가 제시한 3나노 제품의 네 가지 옵션, TSMC가 보유한 3나노 특허 등은 삼성전자가 조기에 극복할 수 있는 부분이 아니며, 따라서 삼성전자가 당장 TSMC를 누르고 글로벌 1위가 될 수는 없다.

또한 삼성전자가 이번 중국업체에 납품할 생산분을 ‘시제양산’이라고 부르고 “2022년 상반기 내에 3나노를 양산하겠다고 했고, 6월 말 시한이 돼서 현재 3나노를 생산하고 있다는 것을 확인해주기 위한 것이다. 본격 양산은 올 연말경 하게 될 예정”이라고 하는 것은 이번 중국 대상 제품 생산이 오리지널 의미의 ‘양산’이 아님을 자인한 것과 같다.

게다가 수율에 대한 구체적 언급이 없는 것은 4나노보다 진보한 3나노니까 수율이 낮을 수밖에 없는 것은 당연하겠지만 동사의 4나노 제품보다 수율이 현저히 낮을 가능성이 있다는 것의 반증으로 볼 수 있다.

이와 관련, TSMC가 삼성전자의 3나노 칩 성능을 “우리 5나노와 비슷한 성능”으로 표현하는 것은 성능과 개선점에 대한 비판임과 동시에 TSMC도 3나노 수율문제는 거론하기 어려울 정도로 난항을 겪고 있는 것이라는 시각도 있다.

사실 삼성전자는 몇 가지 분명한 약점들을 가지고 있다. 예컨대 ▲삼성전자 3나노 칩의 개선비율 비교 대상이 동급의 TSMC 제품보다 성능이 훨씬 떨어지는 5LPE라는 점 ▲팰리클 채택 이전에는 TSMC보다 수율이 뒤질 수밖에 없다는 점 ▲수율 개선이 전 공정에서 팰리클을 채택할지 여부 외에도 후공정에서 어떤 노하우를 갖고 있는 지도 영향을 미쳤을 것이라는 점 ▲TSMC에 비해 훨씬 처지는 생산능력 등이 그것이다.

이처럼 삼성전자의 약점이 분명해 보이지만 앞으로 삼성전자가 과연 이런 약점들을 얼마나 슬기롭게 대처해 나갈지 지켜봐야 할 것이다.